半導体用語集

演算増幅器

英語表記:operational amplifier

演算増器の機能モデルには、増幅器としてC言語で定数の掛け算をするモデルの他、 VHDL-AMSやVerilog-AMSなどの混載シミュレータで用いるモデルの2種類ある。おのおののシミュレータにはテンプレートの形でいくつか用意されている。記述方法はそれぞれのソフトウェアのマニュアルを参照されたい。その他、SPICEシミュレーションでも、ゲート/ソース電圧が変化するものは制御電圧源で、定電流源を電流源と置き換えるこ とにより、シュミレーション時間を短縮できる。

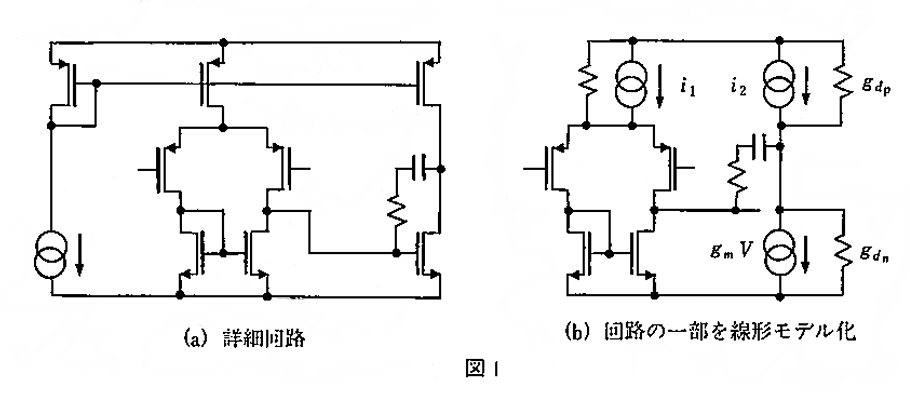

SPICE シミュレータに用いるモデルは、詳細なシミュレーションを行いたい がシミュレーション時間が長くなりすぎる時に用いられる。主に入力段 の電圧マージンや出力に負荷を接続した時の演算増幅器を含む回路全体の振る舞いを検証する時に用いられる。たとえば入力段の電圧マージンを調べるのであれば、図1に示すようにに入力段の回路だけトランジスタを用いた回路記述で、後は電圧制御電流源などを 用いて記述する。このような記述を行 うことにより、接点数や非線形モデル計算回数を削減して収朿性の向上と計算時間の削減を図ることができる。

VHDL-AMSなどのシミュレータでは、直流利得や極の周波数など周波数領域での応答特性とスルーレートなど演算増幅器の仕様で記述することができる。シミュレータ内では、この記述を電圧制御電流源などの抽象的な回路に置き換えてSPICEと同様な方法 で計算を行う。

関連製品

「演算増幅器」に関連する製品が存在しません。キーワード検索

フリーワードやカテゴリーを指定して検索できます

関連用語

関連特集

「演算増幅器」に関連する特集が存在しません。

会員登録すると会員限定の特集コンテンツにもアクセスできます。