半導体用語集

演算増幅器

英語表記:operational amplifier

アナログコンピュータの基本素子として生み出された。一般的には、正負の入力の差だけを大きい利得で増幅し、同相成分は抑圧する機能を持っている。正確な増幅率で増幅する時や、フィルタなどを構成するための基本素子である。

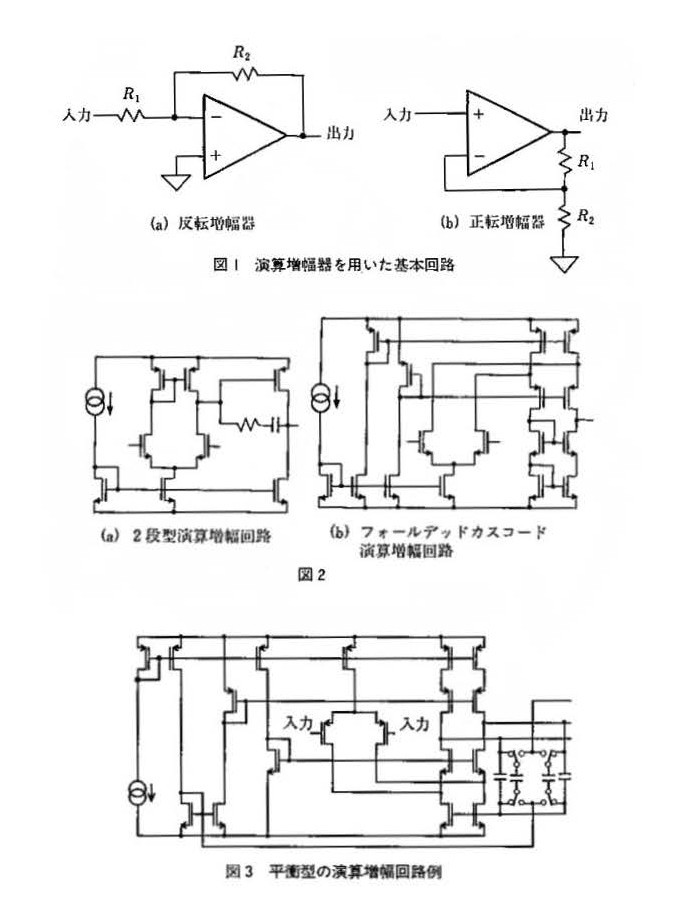

これを用いた増幅回路には入力と出力の関係が、極性を反転した増幅とそうでない増幅(正転)の2種類あり、構成方法を図1に示す。反転増幅器の利得は演算増幅器の利得が十分大きければこの回路の利得は-R₂/R₁と抵抗比だけで決まる。この形式は、演算増幅器の反転入力点が正転入力端子の接地電圧にほほ等しい状態で動作するので、演算増幅器の入力電圧範囲は小さくてすむ特徴がある。その代わり、入力インピーダンスとしてR₁が直接みえる。この結線の反転入力は仮想接地点と呼ばれる。正転増幅を構成した時、利得は1+R₁/R₂となる。正転増幅は出力が入力に追随するように動作するので、電圧フォロアとも呼はれる。この場合には出力が入力に追従するので、演算増幅器の入力範囲は広くなければならない。そのかわり、入力にはゲート容量がみえるだけであるので、入力インピーダンスは高い。

入力電圧範囲は演算増幅回路の入力段の回路形式で大きく左右される。回路形式の主なものにはアクティブ負荷の差動型とフォールデッドカスコード型があり、入力トランジスタをnMOSとするか、pMOSとするかの選択がある。同時に応用回路として用いる回路形式によっても要求仕様は変わる。

出力電圧範囲が広い時には差動段と利得段を持った2段型の回路が選ばれ るが、出力電圧範囲が狭い時にはカスコード1段の回路でも仕様を満たすこ とができる。

入力オフセット電圧は、特に入力ト ランジスタのしきい値電圧および相互コンダクタンスのばらつきで生じる。MOS回路でも数mV以下にすることは可能であるが、たとえ、1μm以下の加工精度を有するプロセスを用いても、トランジスタのチャネル長を数ミ クロン以上で設計する必要がある。また、トランジスタの配置の影響を大きく受ける。

オープンループ利得は、開ループで演算増幅器を動作させた時の直流での差動利得である。応用回路を組んだ時、理想状態からの誤差に影響する。

ユニティゲイン周波数は演算増幅器を開ループで動作させた時、利得が1となる周波数。応用回路を組んだ時、周波数特性やダイナミック特性での誤差に影響する。

位相余裕はユニティゲイン周波数で出力位相回転を、180度から差し引いた値で、閉ループ回路を組んだ時、ステップ電圧の変化に対してどれだけ早く電圧が定まるかの指標となる。応用回路を組んだ時、ダイナミック特性での誤差に影響する。スイッチトキャパ シタ回路では少なくとも60度は必要である。

利得余裕は出力位相が180度回転する入力局波数での利得で、回路によってはユニティゲイン周波数より高い周波数で利得が高くなることがあるので、それがないことを示す指標である。

スルーレートは、利得が1の反転増幅または正転増幅接続してステップ電圧を加えた時、出力がほぼ一定傾斜で変化する変化率を示す指標である。ステップ入力に対して静定する時間を決定づけるパラメータである。スイッチトキャパシタ回路を組んだ時、ダイナミックなセトリング誤差に影響する。大信号出力帯域は、出力電圧範囲の上限に近い振幅の正弦波を出力する時、その周波数の上限を規定するパラメータで、通常は3dB利得が低下する周波数を指す。スルーレートで制限を受ける。出力振幅を大きくした時の歪を表わす指標でもある。大きくするためには消費電力の増大となる。

小信号出力帯域は小信号の正弦波に対する周波数の上限を規定するパラメータであり、ユニティゲイン周波数で制限を受ける。

同相信号除去比は差動利得と同相利得の比である。この作用があることを利用して、集積回路内でのアナログ配線に誘導される雑音を正負の入力で等しくなるように配置することで、誘導雑音が信号に混入するのを防ぐ。

電源電圧除去比は電源電圧を変動させた時出力にどれだけ影響を与えるかの指標である。集積回路内で電源配線を複数の回路ブロックで共用すると電源線の抵抗やボンディングワイヤのインダクタンスなどによる電源電圧変化は避けられない。そこで、設計においては、この特性を高めた設計を行うか、電源線をブロックごとに分離して行うかを判断する必要がある。回路形式により、正の電源変動に強い回路と負の電源変動に強い回路がある。

入力換算雑音は、入力を無信号とした時、出力に現われる雑音を入力に置き換えたとした時の雑音値で、主として演算増幅回路の入力段の設計で決まる。全高調波歪は目的の使用条件における正弦波入力に対する基本波と高調波成分の比となる。

混変調歪は等しい振幅の相近接する二つの周波数の正弦波を入力した時、出力に現われる差の周波数、もしくは和の周波数成分のどちらか大きい方の振幅と比をとり㏈表示したもの。

これらの仕様項目は用いる回路形式とおのおののトランジスタの寸法、電流により変化する。集積回路に組み込む演算増幅回路には、シングルエンデッド型と平衡型の2種類がある。シングルエンデッド型は、入力は正負2入力で出力は差を増幅して出力する一つの出力端子を持つプリント基板の時代からよく用いられてきたものである。

一方、平衡型は、入力は正負2入力であるが、出力は正負2極性の二つの出力端子を持つ。したがって、応用回路を構成する時、正負に対して対称な回路構成を取ることができる。そのため、回路規模は大きくなり、消費電力も大きくなるが、誘導雑音の影響は小さくできる。また、出力振幅を2倍にできるのに対し素子雑音は正負の入カ換算で相関がない成分に関しては√2倍にとどまるので、3dB改善する。

シングルエンデッドの回路例を図2(a)(b)に示す。これらの回路はいろいろな差動増幅回路と反転増幅器の組み合わせになっている。図(a)の回路は、アクティブ負荷の差動増幅回路に定電流源を負荷とする反転増幅回路によりさらに利得を稼いでいる2段型の演算増幅回路である。2段目の入力と出力を結合している抵抗と容量は位相保証回路で、抵抗は正の実数部を持つ極を防ぐためにMOS回路では必要となる抵抗である。

図(b)の回路は、フォールデッドカスコード1段の演算増幅回路で,カスコード接続することにより2段分の利得がえられる。差動入力段の左側はバイアス回路である。

平衡型の演算増幅回路例としてフォールデッドカスコード1段の回路を図3示す。平衡型の回路は出力の動作点を決める回路を別につける必要があり、ここではスイッチキャパシタの同相フィードバック回路が付加されている。

関連製品

「演算増幅器」に関連する製品が存在しません。キーワード検索

フリーワードやカテゴリーを指定して検索できます

関連用語

関連特集

「演算増幅器」に関連する特集が存在しません。

会員登録すると会員限定の特集コンテンツにもアクセスできます。