半導体用語集

ゲートアレー

英語表記:gate array

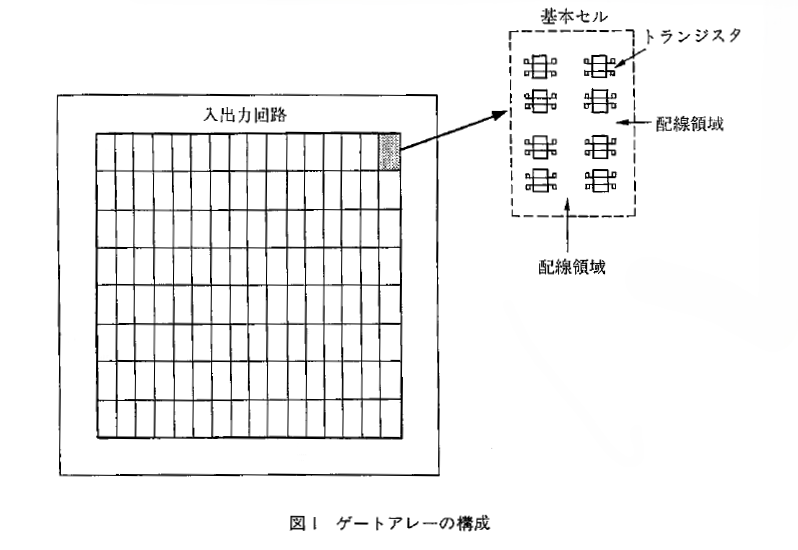

図1に示すように、トランジスタ(および抵抗)と、配線領域から構成される基本セルを二次元に配置し、周辺に入出力回路用トランジスタ(および抵抗)を付加した基板を共通に用意しておき、配線のみの設計により種々の LSIを実現する方法。フルカスタム設計と比較して、設計工数の大幅な削減が図れるが、トランジスタの使用効率が100%ではないため集積度は劣る。ゲート回路が構成しやすいようにトランジスタの数が決められている。化合物半導体電子デバイスについては、GaAs MESFETあるいはGaAs HEMTを用いたものが開発され、 GaAs HBTを用いたものの研究報告がなされている。FET系では低消費電力化に適したDCFLゲートを基本としたものが多い。0.6µmゲートHEMTを用いた基本遅延時間35psの45kゲートアレーが開発されている。HBTではECLゲートが使用され消費電力制限のためゲート数は1kに留まっている。応用例として、スーパーコンピュータのプロセッサ、通信用LSI、コンピュータ間通信用データ送受信LSIなどがあげられる。

参考文献

1) S. Notomi, Y. Watanabe, M. Kosugi, I. Hanyu, M. Suzuki, T. Mimura, and M. Abe:

"A 45 K-gate HEMT array with 35-ps DCFL and 50-ps BDCFL gates", IEEE J.Solid-State Circuits, vol. 26, no. 11, pp.1621~1625 (1991)

2) N. Hayama, Y. Tomonoh, H. Takahashi and K. Honjo : "A 1-K ECL gate array implemented with fully self-aligned AlGaAs/GaAs heterojunction bipolar transistors", IEICE Trans. Electron., vol. E75-C, no.10, pp.1121~1126 (1992)

関連製品

「ゲートアレー」に関連する製品が存在しません。キーワード検索

フリーワードやカテゴリーを指定して検索できます

関連用語

関連特集

「ゲートアレー」に関連する特集が存在しません。

会員登録すると会員限定の特集コンテンツにもアクセスできます。