半導体用語集

歩留り

英語表記:yield

LSI製造の各工程において投入数に対する工程終了後の良品数の割合。ウェハプロセスではウェハ製造工程投入時の枚数に対して、ウェハ割れや工程内検査で不合格となったウェハなどを除いた、完成ウェハ枚数の割合であるウェハ歩留りと、その後のプローブ検査で1枚のウェハから良品としてえられる最大有効チップ数に対する実良品数の割合であるチップ歩留りの積が歩留りとなる。組立プロセスにおいてはプローブ検査で合格となったチップ数に対して、ダイシング以降最終検査までの完全良品数の割合を指す。

歩留りはLSI製造コストに直接関係し、歩留り予測や向上が製造メーカーにとって最重要課題であることはいうまでもないが、その決定要因は多岐にわたっている。特に原因特定が難しいウェハ製造工程における歩留り要因は、回路設計要因、パターン設計要因、そしてプロセス要因に大別することができる。プロセス要因はさらにプロセスパラメータ規格はずれと欠陥に分類される。

歩留りと欠陥(マスク欠陥などによる固定欠陥は除く)については、歩留り予測のために多くのモデルが提案されている。最も基本的なポアソンモデルでは、欠陥がランダムに存在すると仮定し、その発生がポアソン分布に従うとして歩留りを推定している。この場合、歩留りをY、平均欠陥密度をD₀、有効チップ面積をAとすると、

Y = exp ( -D₀A )

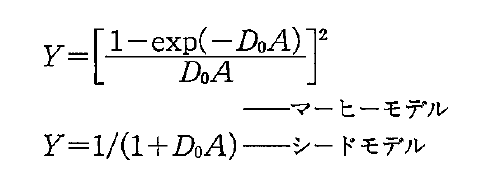

と表わせる。このモデルの改良修正版として、マーヒーモデル(Murphy's model)やシードモデル(Seed's model)などが提案されているが、いずれにしろ欠陥密度やチップ面積が増せば、歩留りは著しく低下することから、今後の微細化の中、パーティクルを中心とした製造プロセス中の欠陥低減対策の重要性はますます大きくなると予想される。

関連製品

「歩留り」に関連する製品が存在しません。キーワード検索

フリーワードやカテゴリーを指定して検索できます

関連用語

関連特集

会員登録すると会員限定の特集コンテンツにもアクセスできます。